Graduate Theses, Dissertations, and Problem Reports

2001

# Electrochemical fabrication of semiconductor nanostructure arrays for photonic applications

Stephen Patrick McGinnis West Virginia University

Follow this and additional works at: https://researchrepository.wvu.edu/etd

#### **Recommended Citation**

McGinnis, Stephen Patrick, "Electrochemical fabrication of semiconductor nanostructure arrays for photonic applications" (2001). *Graduate Theses, Dissertations, and Problem Reports.* 1453. https://researchrepository.wvu.edu/etd/1453

This Dissertation is protected by copyright and/or related rights. It has been brought to you by the The Research Repository (a) WVU with permission from the rights-holder(s). You are free to use this Dissertation in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you must obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/ or on the work itself. This Dissertation has been accepted for inclusion in WVU Graduate Theses, Dissertations, and Problem Reports collection by an authorized administrator of The Research Repository (a) WVU. For more information, please contact researchrepository(a) mail.wvu.edu.

### **Electrochemical Fabrication of Semiconductor Nanostructure Arrays for Photonic Applications**

by

### Stephen Patrick McGinnis

Dissertation submitted to

The College of Engineering and Mineral Resources at WEST VIRGINIA UNIVERSITY

in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering

Biswajit Das, Ph.D., Chair Nancy Giles, Ph.D. Lawrence Hornak, Ph.D. Mark Jerabek, Ph.D. Charter Stinespring, Ph.D.

Lane Department of Computer Science and Electrical Engineering Morgantown, West Virginia 2001

#### **ABSTRACT**

## **Electrochemical Fabrication of Semiconductor Nanostructure Arrays for Photonic Applications**

#### **Stephen Patrick McGinnis**

Theoretical and experimental investigations of the properties of semiconductor nanostructures have been an active area of research due to the enhanced performance that is observed when electrons and holes are spatially confined in one, two or three dimensions. However, the development of viable photonic devices using this phenomenon requires the development of appropriate fabrication techniques that can provide control over nanostructure size, material composition, and periodicity for structures with dimensions less than 20 nm. To address these challenges, a nanostructure synthesis technique has been developed that is based on the self-organization of nanometer scale pores during the anodization of aluminum thin films. This template can then be used for direct synthesis of semiconductor material, or as a pattern transfer mask for the etching of structures in a semiconductor substrate.

In this work, alumina template technology has been transferred from the exclusive use of an aluminum substrate to a thin film technology that can be applied to an arbitrary substrate material. This thin film process has been developed and characterized to permit control and uniformity over both nanostructure length and diameter. In addition, a Al/Pt/Si structure has been developed to permit direct DC synthesis of semiconductor nanostructures. Finally, the ability of this template to serve as a mask for direct etching of nanoscale features on a semiconductor substrate has been evaluated. This technology is currently being developed to provide device applications in the area of photovoltaic devices and silicon electro-optic modulators.

#### **Acknowledgments**

I would like to thank Dr. Biswajit Das, my advisor, for his guidance, instruction and encouragement throughout this research project. I would also like to thank the members of my committee, Dr. Nancy Giles, Dr. Lawrence Hornak, Dr. Mark Jerabek, and Dr. Charter Stinespring for their assistance in this research. Lijun Wang of the Department of Physics at WVU provided valuable PL and Raman data. Professor Albert Miller and Michael Crouse provided great assistance with the electrochemical aspects of this work including material synthesis. I would also like to gratefully acknowledge the assistance of Kolin Brown, Jeremy Dawson, Paul Sines, Christopher Garman, and Dan Gray in the Lane Department of CSEE at WVU.

This work was supported by the National Science Foundation, the National Renewable Energy Laboratory, the National Energy Technology Laboratory and the International Microelectronics and Packaging Society.

Finally, I would also like to thank my family for their assistance and support during my entire education.

## **Table of Contents**

| Abst                               | ii                                                |                                                  |    |  |

|------------------------------------|---------------------------------------------------|--------------------------------------------------|----|--|

| Acknowledgments  Table of Contents |                                                   |                                                  |    |  |

|                                    |                                                   |                                                  |    |  |

| 1                                  | Introduction                                      |                                                  |    |  |

|                                    | 1.1                                               | Competing Nanostructure Fabrication Technologies | 2  |  |

|                                    | 1.2                                               | Alumina Template Approach                        | 10 |  |

|                                    | 1.3                                               | Problem Statement                                | 12 |  |

|                                    | 1.4                                               | Dissertation Outline                             | 13 |  |

| 2                                  | Alumina Template Fabrication and Characterization |                                                  |    |  |

|                                    | 2.1                                               | Bulk Alumina Formation                           | 16 |  |

|                                    |                                                   | 2.1.1 Pore Self-Organization                     | 19 |  |

|                                    | 2.2                                               | Alumina Thin Film Templates                      | 21 |  |

|                                    | 2.3                                               | Standard Process Flow                            | 30 |  |

|                                    | 2.4                                               | Template Characterization                        | 31 |  |

|                                    |                                                   | 2.4.1 Imaging                                    | 32 |  |

|                                    |                                                   | 2.4.2 Electrical Characterization                | 35 |  |

|                                    |                                                   | 2.4.3 Optical Characterization                   | 37 |  |

|                                    | 2.5                                               | Silicon Carbide                                  | 39 |  |

| 3                                  | Electrochemical Synthesis                         |                                                  | 41 |  |

|                                    | 3.1                                               | Chemical Deposition                              | 41 |  |

|                                    | 3.2                                               | Nonaqueous AC Deposition                         | 42 |  |

|                                    | 3.3                                               | DC Nonaqueous Deposition                         | 47 |  |

| 4      | Silico | on Nanostructure Fabrication                  | 49 |

|--------|--------|-----------------------------------------------|----|

|        | 4.1    | Template Based Formation of Porous Silicon    | 49 |

|        |        | 4.1.1 Porous Silicon                          | 50 |

|        |        | 4.1.2 Experimental Method                     | 52 |

|        |        | 4.1.3 Characterization                        | 53 |

|        |        | 4.1.4 Analysis                                | 57 |

|        | 4.2    | Pattern Transfer                              | 59 |

|        | 4.3    | Silicon Nano-Pillars                          | 62 |

| 5      | Photo  | 66                                            |    |

|        | 5.1    | Multijunction Nanostructure Photovoltaic Cell | 66 |

|        |        | 5.1.1 Analysis                                | 69 |

|        | 5.2    | Silicon Surface Texturing                     | 72 |

|        |        | 5.2.1 Subwavelength Structured Surfaces       | 73 |

|        |        | 5.2.2 Fabrication                             | 74 |

|        | 5.3    | Summary                                       | 75 |

| 6      | Concl  | lusions and Future Work                       | 77 |

| Refere | ences  |                                               | 79 |

| Apper  |        | 94                                            |    |

| Apper  | 103    |                                               |    |

## **List of Figures**

| Figure 1-1: Top view and cross-sectional view of alumina pore structure                              | 10 |

|------------------------------------------------------------------------------------------------------|----|

| Figure 1-2: FESEM image of highly ordered pores on bulk aluminum.                                    | 10 |

| Figure 2-1: Schematic of the Keller model for pore formation in anodic alumina.                      | 17 |

| Figure 2-2: Voltage time characteristics during anodization of bulk aluminum                         | 18 |

| Figure 2-3: AFM Image of deposited aluminum film.                                                    | 22 |

| Figure 2-4: Potential time characteristic for template anodization on silicon.                       | 23 |

| Figure 2-5: FESEM image showing silicon oxide formed during anodization.                             | 24 |

| Figure 2-6: Experimental determination of anodization rate as a function of current density          | 25 |

| Figure 2-7: Potential time characteristic for the alumina formation on an ITO coated glass substrate | 27 |

| Figure 2-8: Top view of alumina pores formed on the Al/Pt/Si structure.                              | 28 |

| Figure 2-9: Cross-sectional image showing pores contacting the Pt layer.                             | 29 |

| Figure 2-10: TEM image of pores in alumina. Average pore diameter is 13 nm.                          | 32 |

| Figure 2-11: LEO 1530 FESEM micrograph showing pores in an alumina template                          | 33 |

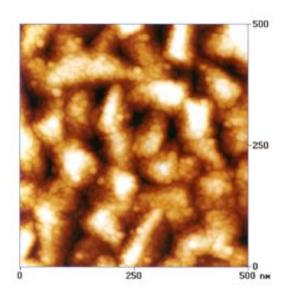

| Figure 2-12: AFM image of an alumina template.                                                       | 34 |

| Figure 2-13: A typical sample for CV measurements. Small circular pads are aluminum top contacts.    | 35 |

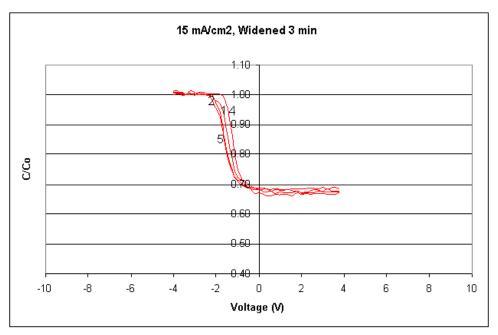

| Figure 2-14: A typical Capacitance-voltage characteristic for the template.                          | 36 |

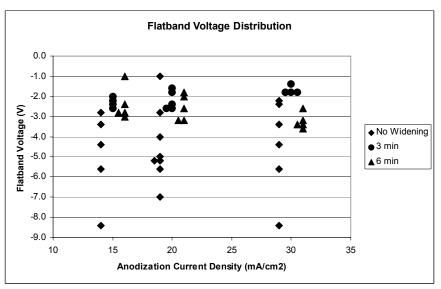

| Figure 2-15: Flatband voltages obtained from CV data of pore-widened and pore-unwidened samples.     | 37 |

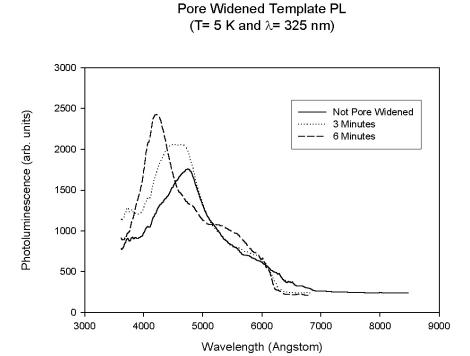

| Figure 2-16: Photoluminescence characterization of pore-widened samples.                             | 38 |

| Figure 2-17: Typical voltage time curve for anodization on a SiC substrate                           | 40 |

| Figure 2-18: FESEM top image of nickel deposited in the pores of alumina thin film template          | 40 |

| Figure 3-1: FESEM Image of 40 nm CdS quantum wires with alumina template removed                     | 43 |

| Figure 3-2: 40 nm CdS wires with the alumina template completely dissolved.                          | 44 |

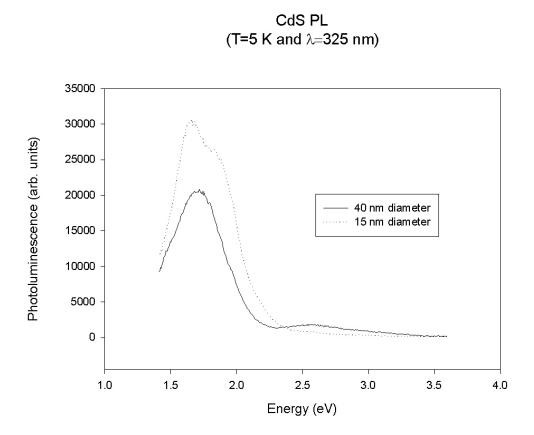

| Figure 3-3: PL characterization of CdS wires with diameters of 40 and 15 nm.                         | 45 |

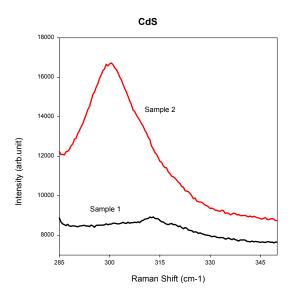

| Figure 3-4: Raman shift of CdS quantum wires with 15 nm (Sample 2) and 40 nm (Sample 1) diameter ne  | ar |

| the first LO phonon.                                                                                 | 46 |

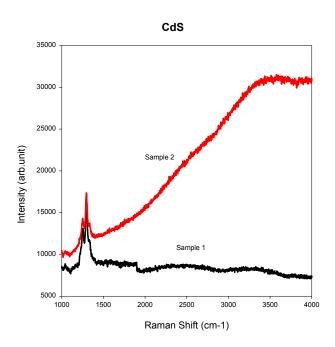

| <b>Figure 3-5:</b> Raman shift of CdS quantum wires with diameters of 40 nm (Sample 1) and 15 nm (Sample 2). |

|--------------------------------------------------------------------------------------------------------------|

|                                                                                                              |

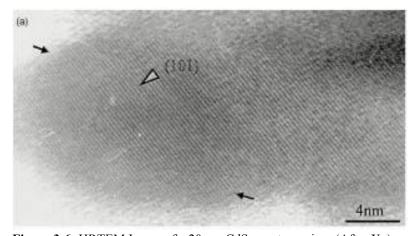

| <b>Figure 3-6:</b> HRTEM Image of a 20 nm CdS quantum wire. 47                                               |

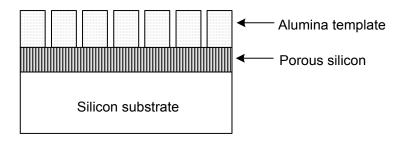

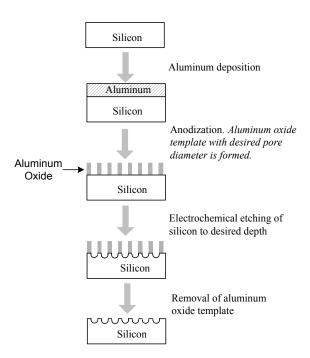

| Figure 4-1 Schematic cross-section showing the formation of porous silicon through the pores of an alumina   |

| template                                                                                                     |

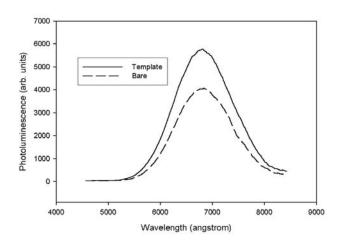

| Figure 4-2 Room temperature PL of PS anodized at 40 mA/cm2.                                                  |

| Figure 4-3: Low temperature PL of PS anodized at 40 mA/cm2.                                                  |

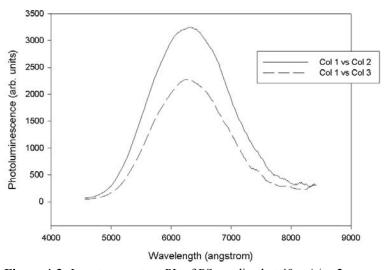

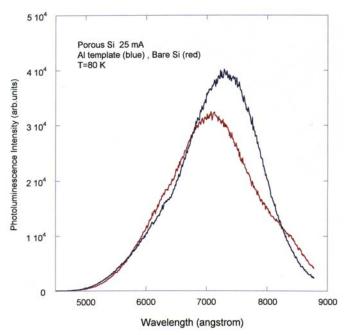

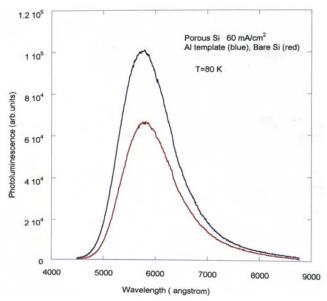

| <b>Figure 4-5:</b> PL (80K) of PS formed at 60 mA/cm2                                                        |

| <b>Figure 4-4:</b> PL (80 K) of PS anodized at 25 mA/cm2                                                     |

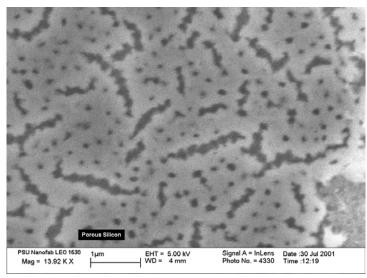

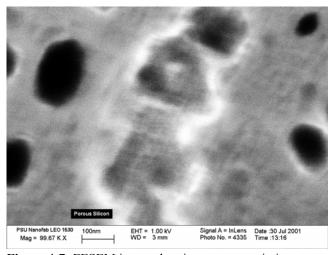

| <b>Figure 4-6:</b> FESEM image of hydrolized alumina template after porous silicon formation                 |

| <b>Figure 4-7:</b> FESEM image showing pores remain intact after porous silicon formation                    |

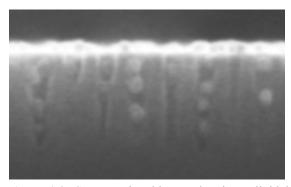

| <b>Figure 4-8:</b> Cross-sectional image showing colloidal particles deposited into silicon pores            |

| <b>Figure 4-9:</b> FESEM top view showing colloidal particles in silicon pores                               |

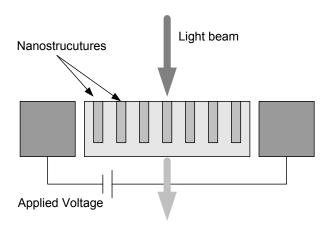

| <b>Figure 4-10:</b> Schematic cross-sectional view showing electro-optic modulator based on QCSE 61          |

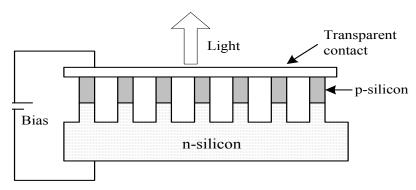

| <b>Figure 4-11:</b> Cross-section schematic of silicon nano-pillar light emitting device                     |

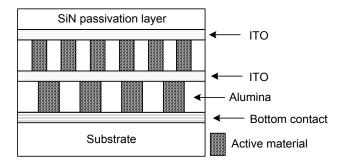

| Figure 5-1 Schematic cross-section of a multi-junction photovoltaic cell                                     |

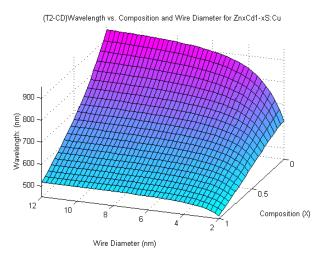

| Figure 5-2 Peak absorption wavelength of ZnCdS quantum wires as functions of wire diameter and alloy         |

| composition                                                                                                  |

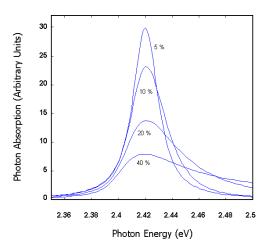

| Figure 5-3 Effect of size distribution on the absorption spectra of CdS quantum wires. Mean wire diameter    |

| : 8 nm 71                                                                                                    |

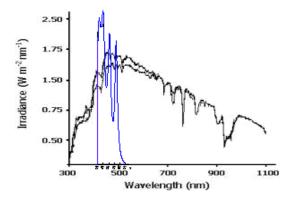

| Figure 5-4 Absorption spectra of 8 nm diameter CdS quantum wires superimposed on solar spectra 72            |

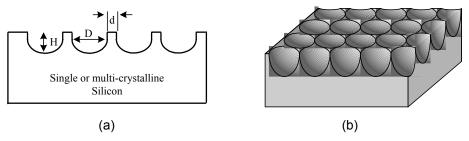

| Figure 5-5 Subwavelength surface texturing of silicon solar cells : (a) cross-sectional and (b) perspective  |

| views                                                                                                        |

| <b>Figure 5-6</b> Process-flow for surface texturing of mono- and poly- crystalline silicon                  |

#### Chapter 1

#### Introduction

The development of nanoscale semiconductor devices has been the focus of increasing scientific research during the past 25 years. This high degree of interest is due to the strong enhancement of electronic and optical properties that occurs when electrons are strongly confined in one, two or three dimensions [1]. This research effort has demonstrated that no single fabrication technique is universally applicable for the production of nanometer scale semiconductor devices. Electron-beam lithography [2-4], atomic beam holography [5], and scanning probe lithography [6] are considered to be the preferred methods for the fabrication of low dimensional *electronic* devices [7, 8]. However, for low dimensional *photonic* devices, the use of "nanogrowth" techniques is being investigated to complement the more traditional fabrication methods. These nanogrowth techniques capitalize on the self-patterning of natural systems where the semiconductor material is synthesized in the size and shape of the desired nanostructure. These methods include fabrication of nanostructure arrays using self-organized epitaxial growth [9-14], chemical synthesis of colloidal nanostructures [15-20], synthesis of nanostructures in glass and polymer materials [21-26], and template based chemical synthesis of nanostructures [27-32].

In the specific area of nanoscale optoelectronics, one of the priorities identified by the National Nanostructure Initiative is to develop "new approaches to synthesis and processing that will lead to affordable commercial fabrication [33]". To meet this goal, it is important to closely tailor fabrication techniques to device requirements and to consider commercial fabrication issues at all stages of research and development. With this in mind, an ideal template for photonic applications should provide: (a) good pore size control and periodicity, (b) good structural and mechanical integrity, (c) chemically inert material for a wide variety of deposited active materials, (d) easily manipulated template size parameters, (e) an economical fabrication process and (f) high transparency over a wide range of the optical spectra. This dissertation will focus on the development of a *thin film porous alumina template* based nanostructure synthesis technique that has the potential to meet the requirements listed above.

#### 1.1 Competing Nanostructure Fabrication Technologies

As mentioned previously, numerous techniques for the fabrication of nanometer scale structures have been developed. Each of these techniques provides a unique strength for a particular application area. In this section, the most popular current techniques will be reviewed and their strengths and weaknesses highlighted.

#### **Porous Silicon**

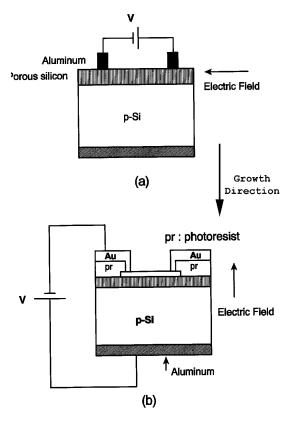

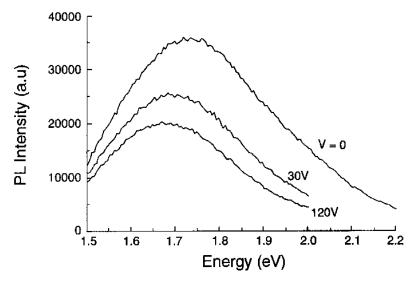

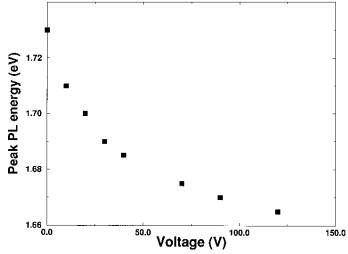

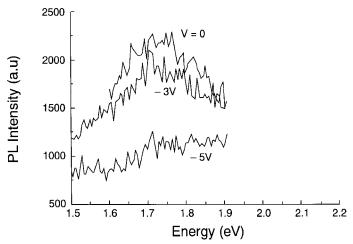

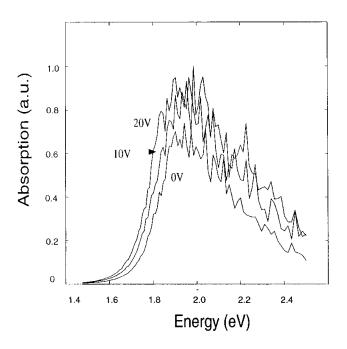

The closest competing technology, and the inspiration for the alumina template technique, is the electrochemical anodization of silicon to form porous silicon. Porous silicon (PS) has been the subject of continuous theoretical and experimental investigations since the first observation of room temperature visible photoluminescence from this material in 1990[34]. Much of this investigation has centered on determining the exact mechanism of light emission in PS, with quantum size effect and emission from Siloxene considered to be the most likely candidates [35]. Recent observations

of continuous tuning of the photoluminescence (PL) spectra with porous silicon nanostructure size [36], the correlation between PL blue shift and radiative lifetime [37], and the observation of transverse-optical (TO) photon replicas in resonantly-excited PL spectra [38] indicate that the quantum size effect is at least partly responsible for producing the observed luminescence in porous silicon. These results are supplemented by the observation of a shift in the PL and absorption spectrum of porous silicon with an applied electric field consistent with the Quantum Confined Stark Effect (QCSE). This result is discussed in more detail in Appendix A [39].

Porous silicon is fabricated by the electrochemical anodic etching of crystalline silicon in an HF solution. The resulting material structure has best been described as an interconnected network of nanoscale silicon structures with varying size and dimensionality [40]. As a result of this size variation, porous silicon shows a broad emission band as a function of wavelength (on the order of 300nm). The lack of a narrow emission linewidth, coupled with the delicate physical nature of the porous silicon structures has limited device applications using this material. Phillip Fauchet at the University of Rochester has demonstrated the integration of room temperature LEDs with silicon bipolar junction transistor devices [40]. However, the lifetime of the optically active structures is not reported. The primary degradation mechanism for porous silicon is an "aging effect" related to oxidation of the silicon nanostructures [40]. Due to the size (~ 2 nm) and large surface are of the nanostructures, native oxide formation can significantly degrade device performance by causing a relatively large change in material diameter. Perhaps the most promising application for porous silicon is its use as an integrated visible and infrared optical waveguide material with reported losses down to 1 dB/cm [41, 42], or as an anti-reflection coating for crystalline silicon photovoltaic cells.

In summary, the porous silicon fabrication technique provides the ability to form highly luminescent structures using an indirect band-gap substrate (silicon). A primary limitation of this approach has

been the inability to identify an appropriate encapsulation material for the porous silicon. As a result, mechanical damage to the nanostructures and chemical aging effects significantly reduce the reliability and operational lifetime of fabricated devices. This technique is compatible with conventional silicon CMOS processing, primarily due to the ability to use conventional photoresists to mask the HF etching process.

#### **Lithographic Techniques**

The traditional and most precise method for nanostructure formation is the use of lithographic techniques coupled with MBE/MOCVD material growth. While electron beam lithogaphy remains the standard nano-pattern definition technique, scanning probe microscopy (SPM) and atomic beam hologaphy have begun to be used for nanoscale device fabrication [3, 43, 44].

The minimum feature size for electron-beam lithography is primarily limited by the resist material used, with a feature size of 7 nm reported using a methylstyrene resist [7]. While this feature size is small in comparison to most devices, it is important to remember that porous silicon is composed of a large number of structures with sizes down to 2 nm, and pores in alumina have been demonstrated down to 4 nm. Therefore, while electron-beam lithography can provide precise placement and definition of small structures, the minimum feature size is still larger than that obtained with other non-lithographic techniques. The second limitation of e-beam lithography is the serial nature of the approach and the Coloumb interaction between electrons in the beam. While a number of attempts to relax these limitations have been proposed [3], none have been able to demonstrate a throughput close to that needed to form dense arrays of individual nanostructures. A final concern with e-beam lithography is defect creation in the semiconductor material from the energy transfer of the electron beam to the substrate material [45]. For the case of semiconductor

nanostructrues, this damage can result in pinning of the Fermi level at the surface, resulting in a variation in the effective electrical size of the nanostructure.

An interesting technique to relax these limitations is the use of atomic beam holography [46, 47]. In this approach, atoms (typically Ne) are cooled to ultra-low temperature (50  $\mu$ K) and diffracted through a computer generated hologram [7]. The potential advantages of this approach are that it can provide nanometer scale lithographic definition ( $\sim$  5 nm) over a large area ( $\sim$ 10 microns) without the use of energetic particles. While this technique is promising, there are several significant limitations. The first is that the minimum feature size actually obtained at present is on the millimeter scale. In addition, this feature size was obtained using a micro-channel plate (MCP) and not with a resist material. As seen with e-beam lithography, the primary limiting factor in obtaining an ultimate minimum size may be the development of an appropriate resist than can provide both feature resolution as well as appropriate resistance to various etch techniques. Finally, the expense of the atomic beam generation and cooling systems (as well as holographic mask fabrication) may limit initial development of this approach. However, the initial capital cost may not be an issue for commercial integrated circuit processing assuming that a sufficient wafer throughput can be maintained.

The most precise method for fabricating nanometer scale structures is the use of scanning probe lithography [6, 44, 48, 49]. Using this technique, semiconductor structures can be patterned by: (a) low energy exposure of resists, (b) thermo-mechanical writing, (c) local oxidation, (d) mechanical modification, and (e) nanomanipulation [6]. The primary limitation of this approach is the extremely low throughput of feature definition. In addition, the definition of nanometer scale features requires the use of an ultra-high vacuum system and substantial vibration isolation equipment. One possible method to improve throughput with this approach is to use a "massively-parallel" arrays of probe

tips. However, no effective method of addressing and controlling such an array of probes has been presented at this time.

In summary, lithographic techniques currently appear to be the most effective method for the fabrication of nanoscale *electronic* devices. This is due to the requirement to produce nanometer-scale structures where device functionality is the result of the interconnection between individual structures. There are no fundamental limitations on size, shape, or composition of the nanostructurses, or on the active materials. The primary limiting factor of these techniques is not necessarily performance, but the ability to generate a low enough cost-of-ownership to enable commercial operation.

#### **Heteroepitaxial Self Assembled Structures**

The primary technique used for the development of quantum dot lasers is the self-assembly of quantum dots during MBE/MOVPE heteroepitaxy [13, 50-60]. This approach relies on non-equilibrium heteroepitaxial growth utilizing a stepped (vicinal) surface as a template [61]. The primary advantage of this approach is the excellent material quality resulting from the MBE/MOVPE growth and the lack of an etching/lithography step that can result in material damage. By varying the growth properties the structures can range from quantum wires to "strings of quantum dots" [61]. While lasing has been demonstrated due to the high material quality, and low threshold has been observed due to the low discrete density of states in quantum dots, these structures tend to have significant inhomogeneous line broadening due to variation in nanostructure size [50].

This approach can provide structures ranging from quantum dots to quantum wires by varying the material deposition properties. The composition of the nanostructures is limited to III-V and II-VI

elements that can be deposited by MOVPE or MBE techniques. In addition, the use of a given substrate material limits the choice of deposited nanostructure material to maintain quantum confinement. As presently constructed, this technique is not compatible with silicon CMOS processing due to the requirement for a stepped (vicinal) substrate to prevent anti-phase disorder (APD) [62].

#### **Colloidal Semiconductors**

The preparation of colloidal semiconductors in solution provides the best method for experimental verification of theoretical results in the physics of nanostructures. Using colloidal techniques, solutions with nearly monodisperse particle size distributions with uniform spherical shape and sizes down to 1.5 nm can be formed [63]. In addition, by coating the particles with an appropriate organic shell [64], electrons or holes can be rapidly removed from the quantum dot, allowing observation of carrier relaxation dynamics by infrared pump-probe spectroscopy. Using this technique, the "phonon bottleneck" in quantum dots was observed for the first time experimentally [65].

Using this technique a number of III-V, IV, and II-VI semiconductor quantum dots have been synthesized in solution. The size distribution is highly uniform and the nanostructures are generally spherical. The primary limitation of this approach is that the colloids are synthesized in solution, and as a result using these structures for device applications has been problematic. Deposition and drying of the solution on a substrate material results in clumping of the individual particles with loss of quantum confinement [15].

#### **Doped Glasses**

One of the oldest methods of semiconductor nanocrystal synthesis has been the heat treatment of a glass host doped with semiconductor precursors (e.g. CdO and Te). After heat treatment homogeneous nucleation of the semiconductor precursors results in the formation of nanocrystals within the transparent host material [21, 22, 66, 67]. Using this approach, nanostructures with good size distribution (~6 %) and small size (~ 3 nm) can be formed. The primary limitation of this approach is the high process temperature required to melt the glass host material, and the lack of control over nanocrystal periodicity.

The advantages of this approach is that it provides quantum dot formation at relatively low cost with excellent encapsulation. However, this encapsulation also limits the ability to contact the nanostructures for detector applications. CMOS applications are limited due to the requirement to deposit the material as a molten glass.

#### **Template Based Approaches**

In addition to the use of an anodized aluminum template, several other template based approaches have been reported. One of the earliest reported non-lithographic nanostructure fabrication techniques is based on the use of track-etched polymer membranes. In this approach, nanometer scale damage paths are formed in a polymer material as the result of irradiation by heavy ions. The resulting damage paths can be etched resulting in pores with diameters down to 30 nm and lengths of up to several microns. Active superconductor and metals can then be deposited in the pores using standard chemical synthesis techniques. The primary application area for this approach has been in the investigation of giant-magnetoresistance effects in metal nanowires [68-70]. The limitations of polymer track membranes are relatively large pore diameters (30 nm), lack of size control, and lack of pore periodicity.

A second approach is the use of zeolite structures as a template for chemical synthesis of semiconductor nanostructures. In particular, the MCM-41 host material has been used to synthesize a number of semiconductor materials including CdSe [32], Si [71], Ge [72], InP [73], GaAs [73], CdS [74], and GaN [75, 76]. MCM-41 provides a hexagonal array of cylindrical pores with diameters down to 2.7 nm and a reported size distribution (FWHM of 0.2 nm) calculated by N<sub>2</sub> desorption data [32]. However, there is no evidence that this technique has been used to form thin films of nanostructures. Instead, the zeolite host material is used in powder form, washed with toluene to remove excess material, and precipitated as a powder with MCM-41 loaded semiconductor nanostructures [32]. According to the various reports, this is done to allow characterization by various analytical techniques. However, it is significant to note that no reference is made to optical characterization of the thin film nanostructure arrays.

The final template based synthesis method to be discussed is the use of carbon nanotubes. Carbon nanotubes have been synthesized in alumina templates to from fixed parallel arrays of nanotubes [77-79]. In addition, there is one report of using a carbon nanotube as a template for chemical synthesis of semiconductor material [80]. However, this tends to be a "template within a template approach" and does not appear to provide significant fabrication or application advantages.

#### **Summary**

A number of semiconductor nanostructure fabrication techniques have been demonstrated that have potential for very specific applications. In particular, the use of lithographic techniques provides the greatest control over size and shape for research applications. However, the development of sufficient throughput for volume production remains the fundamental challenge. Porous silicon remains a popular technique due to its ability to directly provide luminescent structures using a silicon substrate. However, unless the particle size distribution and encapsulation issues are

addressed, this technique does not appear to have significant device applications. Heteroepitaxial techniques are primarily restricted to the development of quantum dot lasers. This approach provides the highest level of material quality, however, size distribution and uniformity are not significantly improved over other less expensive techniques. Doped glasses have been used to demonstrate high performance optical modulators [81] and provide excellent encapsulation of the nanostructures. However, integration issues and poor nanostructure periodicity limit this approach.

#### 1.2 Alumina Template Approach

The primary focus of this dissertation is the development of a non-lithographic fabrication technique based on the electrochemical synthesis of compound semiconductor material using a template of anodized alumina. A basic overview of this technique is presented in this section and is discussed in more detail in Chapters 2 and 3.

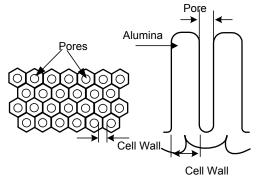

When aluminum is anodized in an appropriate acidic electrolyte under controlled conditions, it oxidizes to form a hydrated aluminum oxide (alumina) containing a two dimensional hexagonal array of cylindrical pores as schematically shown in Figure 1-1. The pore diameter and the inter-

**Figure 1-1:** Top view and cross-sectional view of a schematic of the alumina pore structure.

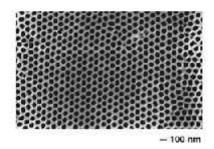

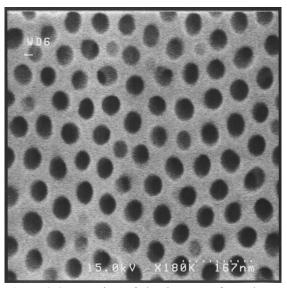

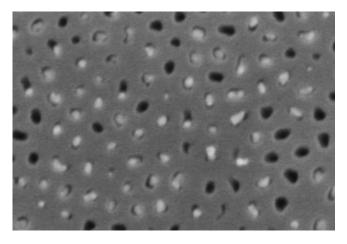

**Figure 1-2:** FESEM image of highly ordered pores on bulk aluminum.

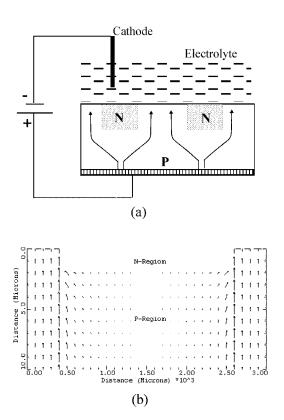

pore spacing depend on the anodization conditions such as electrolyte pH, temperature, anodization current density, and aluminum microstructure (grain size). Pores can be up to several microns in depth. The anodization parameters can be precisely controlled to form pore diameters between 4 and 100 nm with less than 10% variance in the pore size distribution in bulk aluminum (Figure 1-2). As a result anodized alumina can act as ideal templates for the fabrication of periodic semiconductor nanostructure arrays for photonic and electronic applications if similar order can be obtained for thin films. Anodization is performed in a simple wet chemistry apparatus where the aluminum layer is polarized as the anode (positive), and a platinum electrode is used as the cathode (negative).

Anodization can be performed under constant DC current (galvanostatic) or constant DC voltage conditions (potentiostatic). Sulfuric acid and oxalic acid are typically used for the anodization of aluminum. During the first 3-5 seconds of anodization, a thin continuous film of alumina, called the barrier layer, is formed on top of the aluminum substrate. As anodization is continued, an array of pores begins to develop in the barrier layer. The pore diameters increase until reaching a steady state dimension determined by the anodization conditions. When the steady-state diameter is reached, the pores grow in depth at a rate proportional to the anodization current density until the aluminum has been exhausted or until the applied current is removed. Therefore both the pore diameter, which is solely determined by the anodization conditions, and the pore depth, which can be determined from the linear pore formation rate, can be precisely controlled. This allows the properties of the nanostructure to be varied between those of a quasi-spherical quantum dot (confinement in three dimensions) to a quantum wire (confinement in two dimensions). The evolution of the optical and electrical properties of these structures as a function of the confinement dimension has been recently been shown by Susa [82].

The active semiconductor material for the nanostructures is formed by electrochemical synthesis or colloidal deposition inside the pores. The in-situ electrochemical synthesis of active materials within the pores has been well investigated by our group as well as a number of other researchers [83, 84]. Some of the species introduced into the bulk nanoporous alumina are: gold, nickel, iron, CdS, CdTe, ZnS, CdSe, GaAs and ternary semiconductor compounds (Cd<sub>x</sub>Zn<sub>1-x</sub>S). In particular, Cadium Sulfide has been a well-investigated system both by our group and other researchers due to its high degree of optical activity and non-linear optical properties. In addition, the synthesis of narrow band-gap (e.g. InAs) semiconductors through the electrophoretic deposition of colloidal materials is currently being investigated in collaboration with the University of Notre Dame.

#### 1.3 Problem Statement

The formation of semiconductor and metallic nanostructures using alumina templates formed on bulk aluminum substrates has been demonstrated by a number of researchers [77, 78, 80, 85-97]. However the use of an aluminum substrate is problematic for two primary reasons. First, it is difficult to obtain aluminum substrates with a high level of material purity and a low degree of surface roughness. Second, it is difficult to integrate the devices produced with other electronic or photonic components such as transistors or waveguides. Therefore, it is desirable to be able to create templates with high uniformity using an aluminum thin film deposited on an arbitrary substrate material. After templates have been created with a high degree of periodicity and size control, the next concern is the ability to use this to create semiconductor nanostructures with useful properties for device applications. Finally, once arrays of nanostructures have been created, it is necessary to be able to determine if a viable device applications exists for the material that has been created.

To address the challenges in the previous paragraph, three specific research goals have been identified:

- 1) To create and characterize thin film alumina templates on multiple substrate materials.

- 2) To develop a process that enables the synthesis of semiconductor nanostructures with the level of material quality required for photonic applications.

- 3) To identify commercially viable device applications for this technology.

In summary, the primary objective of this dissertation is to determine if the fabrication of semiconductor nanostructures using a preformed alumina template is viable for photonic device applications. Then, given that this objective is met, to lay the foundation for future research using this technique.

#### 1.4 Dissertation Outline

Chapter two will provide an overview of the anodization of bulk aluminum and the extension of this technique to thin film alumina templates on a variety of substrate materials. In addition, the characterization of these templates by imaging, photoluminescence, and electrical techniques will be discussed.

In chapter three, the electrochemical synthesis of compound semiconductor materials into the alumina template pores will be presented. This will include an overview of quasi-electrochemical techniques, AC nonaqueous deposition, DC nonaqueous deposition, and underpotential deposition.

Chapter four will discuss the use of the alumina template to create a pattern transfer mask for the creation of nanostructure in a silicon substrate. Three different techniques to accomplish this will be presented: porous silicon formation, RIE pattern transfer, and RIE image reversal.

Chapter five will present device applications of this technology in the development of photovoltaic devices. In particular, the use of semiconductor nanostructures synthesized in the template pores for the creation of multijunction solar cells will be discussed. In addition, the use of this technique to create subwavelength textured surfaces will be analyzed.

In chapters six and seven the conclusions that can be drawn from this research as well as future work will be presented.

Finally, Appendix A and B will contain previous work in the area of porous silicon not directly related to the major topic of this dissertation.

#### Chapter 2

#### **Alumina Template Fabrication and Characterization**

When aluminum is anodized in an oxidizing electrolyte, a thin layer of hydrated aluminum oxide, or alumina is formed. Depending on the strength of the acidic solution used, field enhanced oxide dissolution can compete with the aluminum oxidation process to from a material with nanometer-scale pores. This property has been used since the 1930's to provide both corrosion protection for aluminum parts as well as to dye these materials. However, during the 1990's it was realized that the pores in alumina could provide a template for the synthesis of both semiconductor and metal nanostructures. In fact the alumina material provides an almost ideal template since it can provide periodic pores with good control over the size distribution, is transparent over the visible spectrum, is electrically insulating, and is relatively corrosion resistant [98]. The primary limitation to the development of photonic devices using this approach has been the requirement to use an aluminum substrate. The objective of this dissertation research has been to by investigating the formation of an ordered porous alumina thin film on an arbitrary substrate material.

In this chapter, alumina formation on bulk substrates will be discussed along with recent work describing the formation of self-ordered structures. Then the extension of this work to semiconductor substrates will be presented. Finally the characterization of these templates using imaging, optical and electrical techniques will be discussed.

#### 2.1 Bulk Alumina Formation

Initial formation of alumina can be the result of a spontaneous reaction between aluminum and oxygen than results in the creation of an insoluble anhydrous aluminum oxide layer. The self-limited formation of this nanometer scale layer can then protect the remaining aluminum from further chemical reaction. Since this is a spontaneous chemical process, it cannot be easily controlled and is assumed to always exist on an aluminum surface. It is for this reason that in aluminum RIE etch procedures, an aluminum oxide etch is conducted before the aluminum etch.

When aluminum is immersed in an electrolyte and a potential is applied, the formation of thicker oxides can take place. In the case of anodization in neutral (pH 7-8) solutions, a non-porous oxide is formed. The thickness of this oxide is limited to several hundred nanometers, after which dielectric breakdown of the oxide creates a short circuit ending the electrochemical reaction [99]. For the case of strong acids (sulfuric, phosphoric, oxalic) field assisted oxide dissolution results in the formation of a close-packed array of columnar hexagonal cells. Due to the porous structure of the films, charge transport takes place only across the barrier layer removing dielectric breakdown as a thickness limiting mechanism.

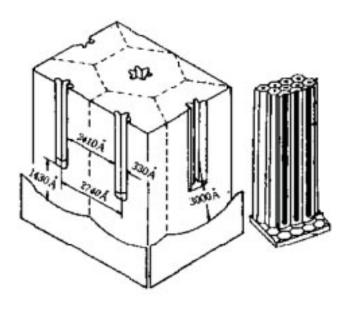

Keller, Hunter, and Robinson first characterized porous alumina as a close-packed array of columnar hexagonal cells each containing a central pore normal to the substrate surface [100]. A schematic of the Keller model is shown in Figure 2-1. While several other models to explain certain aspects of pore formation have also been developed, for this work the Keller model remains the most relevant

**Figure 2-1:** Schematic of the Keller model for pore formation in anodic alumina.

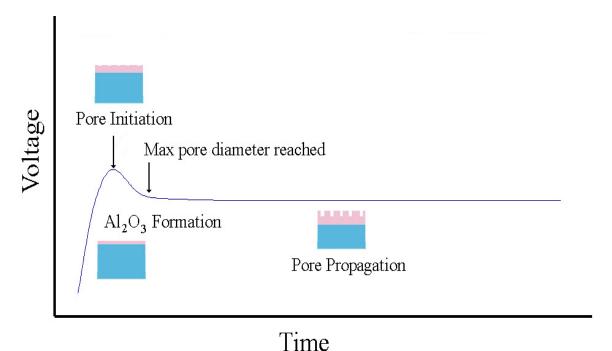

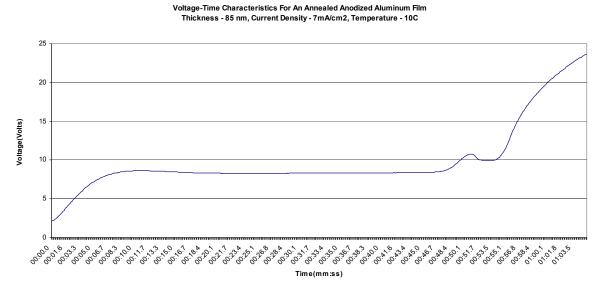

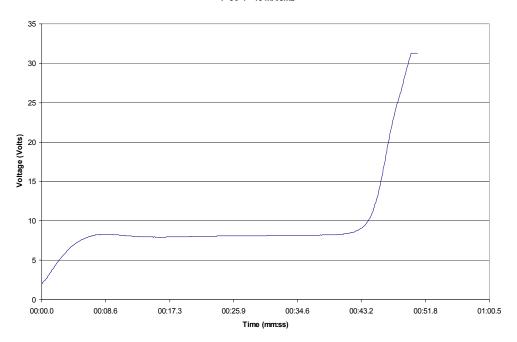

The electrochemical anodization of aluminum to form alumina takes place in several discrete steps. During the first 3-5 seconds of anodization, a thin non-porous film of alumina (Al<sub>2</sub>O<sub>3</sub>) called the barrier layer, is formed on the aluminum surface. As anodization proceeds, an array of pores develops on the barrier layer, whose diameters increase until reaching a final dimension determined by the anodization conditions. Once the final diameter is reached, the diameter of the pores do not increase any further, and as the anodization is continued, the pore depths increase at a rate proportional to the anodization current. A convenient way to monitor the anodization process is to observe the voltage-time characteristics measured between the anode and the cathode. Since the potential across the device is proportional to the device resistance, it increases during the first 3-5 seconds when the high resistance barrier layer is formed. Next, as the pores begin to develop, the

potential decreases until the final pore diameter is reached, after which the potential remains constant as the pores propagate. A schematic of the pore formation process for an alumina thin film on bulk aluminum is shown in Figure 2-2

The initial formation of the barrier layer material is the same for the creation of both porous and non-porous oxides. As the temperature increases, the maximum voltage increases and the position

Figure 2-2: Voltage time characteristics during anodization of bulk aluminum

of this maximum occurs earlier in the anodization process. After this maximum potential is reached, pore nucleation begins at the alumina surface and results in a decrease in the potential until a steady state situation is reached. The initial nucleation of pores on the alumina surface is believed to follow initial roughness in the barrier alumina film [99]. Since the electric field around an asperity is enhanced [101], a non-uniform dissolution of alumina at the electrolyte interface is created.

After pores are nucleated, they reach a final fixed diameter and begin to propagate through the growing aluminum oxide (alumina). The exact mechanism for this behavior is not clear. It has been suggested that ohmic control of the surface at the pore mouth, or an automatic adjustment of surface film properties that stabilizes a fixed pore size [101] is responsible for this effect. For the case of alumina formed using a bulk aluminum substrate, the voltage remains constant until anodization is completed, or until the substrate is completely anodized. Since the electrochemical oxidation front proceeds ahead of pore formation, a barrier layer of thickness equal to the pore diameter separates the pore from the non-oxidized aluminum.

#### 2.1.1 Pore Self-Organization

It has been experimentally observed that as the anodization process continues, the initial randomly nucleated pores begin to organize into a hexagonal array and the pore size distribution is reduced [102]. The mechanism for this behavior is currently believed to result from the formation of repulsive forces between pores due to mechanical stress in the alumina film [103]. In [103] it is shown that the configuration for lowest mechanical stress in the alumina film is a hexagonal array of uniform pores.

There appear to be two methods to obtain highly ordered pore structures in alumina thin films. First, since pore nucleation is determined by electric field variation at the alumina/electrolyte interface, the alumina surface can be pre-patterned to obtain uniform pore nucleation. Second, the natural tendency of the porous alumina to relax to its lowest stress state during anodization can be used to create a highly-ordered hexagonal array of pores.

There have been several significant attempts to provide ordered pore nucleation. Masuda has used a silicon carbide "nano-stamp" to create preferential nucleation sites for pore growth [104]. This technique involves the creation of a SiC master mold on which the desired pore pattern has been created by electron-beam lithography. The master mold is then applied to the aluminum surface at very high pressure (5 ton/cm²). This technique has demonstrated that control of pore nucleation can lead to highly ordered pore structures. However this approach is not viable for device applications since the master stamp is rapidly damaged due to the high pressures used in the pattern transfer process. A second technique is the formation of an ordered structure through electropolishing of aluminum in a perchloric acid solution [105]. This technique has also resulted in the formation of highly ordered pore arrays. Unfortunately, the smallest pore size that can be created with this technique is 50-55 nm due to the electropolishing dynamics. In addition, the high etch rate of electropolishing (~1 micron/sec) makes this technique impractical for thin film applications.

The use of the inherent self-organization in porous alumina films appears to provide a more viable approach for template formation. Very long anodization times (~ days) have demonstrated that as the anodization time approaches infinity, nearly perfect pore order is created [106]. This has been shown even for the case of significant defects in pore nucleation. Using his SiC stamping process, Masuda has recently shown that the alumina templates have the ability to "self-repair" defects in the pore structure after long anodization times [107].

A combination of these two techniques has been developed resulting in a multi-step anodization process [106]. In this approach the aluminum substrate is partially anodized and then the porous alumina is removed in a solution of phosphoric and chromic acid. Due to the presence of chromic acid, there is a high degree of etch selectivity and the remaining aluminum material is not etched. Therefore, the imprint of the pore bottoms remains at the surface of the aluminum substrate. This

is then used as a preferential pore nucleation site for the next anodization cycle. This process can be repeated as many times as necessary given a sufficient aluminum thickness. Since the template is removed, pore organization can proceed at a faster rate and pore order equivalent to the anodization of several millimeters of film can be obtained with a starting material of less than one micron [106].

#### 2.2 Alumina Thin Film Templates

The fabrication of alumina thin films on bulk substrates has demonstrated the feasibility of this approach for nanostructure synthesis. However, for the development of photonic applications, thin film templates with flexibility in the choice of substrate material is desired. In this section, the work to develop the thin film template technology is described. In particular, the methods for thin film deposition, template anodization, and pore widening will be presented. Finally, the development of a platinum/alumina structure will be presented that allows the formation of single crystal semiconductor nanostructures.

#### **Aluminum Thin Film Deposition**

The use of magnetron sputter deposition, thermal evaporation, and electron-beam evaporation were investigated for the creation of aluminum thin films for template fabrication. The first technique attempted was thermal evaporation of 99.999% Al pellets in a thermal evaporation system refurbished by the Nanostructures Research Group [108]. This system is pumped with a Varian diffusion pump and is operated at a base pressure of  $5x10^{-6}$ . The potential-time profile during anodization showed the basic features expected during anodization. However the slow rise in potential during pore propagation is believed to result from non-uniform anodization of the deposited film. In addition, visual inspection of the anodized layer revealed non-uniform adhesion

to the silicon substrate. These effects are believed to result from non-uniform aluminum deposition caused by a problem with the planetary rotation system.

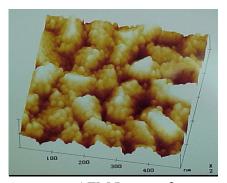

The second method investigated was magnetron sputtering of both 99.999% Al as well as an Al-Cu alloy (99.999% purity.) Sputtering was preformed in a cryo-pumped deposition system in an Argon atmosphere with base pressure of  $1.0 \times 10^{-6}$ . This deposition technique (without substrate heating) resulted in substantial roughness in the deposited aluminum material. An AFM image of the deposited film is shown in Figure 2-3.

The final method used for thin film deposition was electron-beam evaporation of 99.999% Al using a cryo-pumped system at a pressure of  $5x10^{-7}$ . This was accomplished at the University of Notre Dame. This technique appears to provide enhanced uniformity in the deposited layer as well as decreased surface roughness. This technique is currently the primary method of deposition of aluminum thin films in this research except where noted.

Figure 2-3: AFM Image of deposited aluminum film.

#### **Anodization**

Template formation was performed by anodization in a solution of 20% (v/v)  $H_2SO_4$  at a temperature of  $3^{\circ}C$ . The low anodization temperature is used for two reasons. First, Masuda has experimentally demonstrated that low anodization temperature ( $<3^{\circ}C$ ) significantly increases pore uniformity. The second reason is that alumina is weakly soluble in sulfuric acid leading to an undesirable isotropic etching of the alumina pores. This effect can be eliminated by a reduction in the anodization temperature since chemical etching is a thermally activated process. This is similar to the use of a liquid-nitrogen cooled stage during deep-trench silicon RIE to increase etch anisotropy.

A potential time characteristic for anodization on a silicon substrate is shown in Figure 2-4. When compared with anodization on a bulk substrate, the early stages of barrier layer formation, pore nucleation, and pore propagation are not effected. However, a rapid increase in potential is seen as the aluminum oxidation front hits the silicon surface. This feature is unique to anodization on non-aluminum substrates and is strongly dependent on the substrate characteristics (type, doping,

**Figure 2-4:** Potential time characteristic for template anodization on silicon.

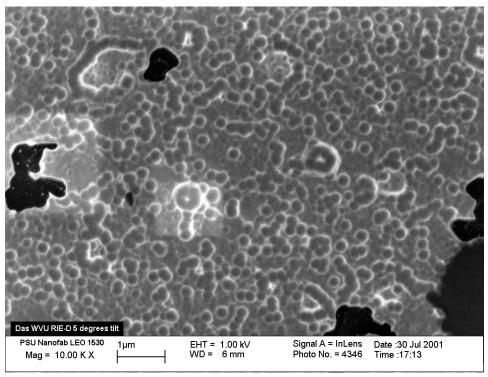

annealing). It is believed that the rapid increase in potential results from the anodic oxidation of the silicon substrate. To verify this theory, an alumina template was formed on a silicon substrate and the anodization current was left on for 15 seconds after the potential reached the maximum allowed by the power supply (30 V). Then, the template was removed by a phosphoric acid etch. Since there is a large degree of etch selectivity between alumina and silicon dioxide (> 100:1), this etch should not have altered any silicon dioxide formed. The substrate was then imaged using a LEO 1530 FESEM at the Penn State National Nanofabrication Users Facility with a representative image shown in Figure 2-5. The detection of a two layer structure and the observation of significant charging strongly suggest that an oxide was formed at the silicon/alumina interface. However, the structural composition and stoichiometry of this oxide have not been determined.

Figure 2-5: FESEM image showing silicon oxide formed during anodization.

A significant advantage of using an alumina template on a silicon substrate is that the anodization rate can be determined by monitoring the time between the initiation of anodization until the rapid rise in potential at the silicon surface is observed. The anodization rate was determined as a function of current density in collaboration with Paul Sines for a variety of anodization temperatures and film thicknesses. These results are shown in Figure 2-6 and indicate a linear dependence between anodization rate and current density, especially at low current densities.

##

Figure 2-6: Experimental determination of anodization rate as a function of current density.

#### **Pore Widening**

Pore widening in 5% phosphoric acid is performed after anodization to remove the top surface of the alumina template where non-uniform pore nucleation has occurred. This technique can also be used to chemically remove the alumina barrier layer as well as to increase the average pore diameter.

One concern during pore widening is to ensure a uniform distribution of the acidic solution within the porous structure to ensure uniform chemical dissolution. To enhance uniform etching, the templates are soaked in de-ionized (DI) water for approximately 12 hours to equilibrate the template and reduce the effect of surface tension at the pore mouths.

#### **Barrier Layer Engineering**

A technological limitation to the development of this template based nanostructure technology is the presence of an alumina barrier layer at the bottom of the pore. This can be chemically etched using the pore widening process, however there is a narrow process window between complete barrier layer removal and complete liftoff of the template. In the case of bulk alumina templates, the barrier layer is detached from the substrate by etching in mercury chloride which also serves to eliminate the barrier layer. A second concern is the formation of an oxide layer on the substrate at the alumina/substrate interface. This was shown previously in the case of silicon, however a similar anodic oxidation (or substantial substrate etching) occurs for most other materials [109].

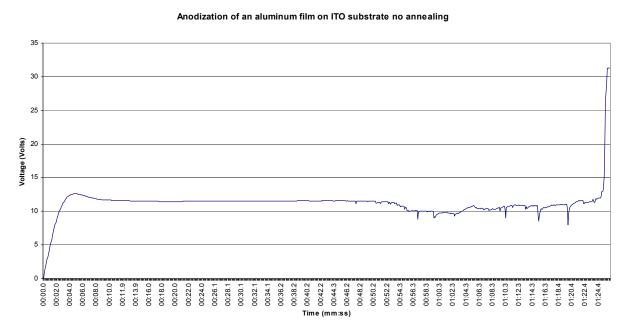

Two approaches were investigated for addressing the barrier layer issue and substrate oxidation. The first approach is to use a conductive oxide (i.e. ITO) as an interfacial layer (i.e., aluminum/ITO/silicon) to prevent oxidation of the silicon surface. Previous work tends to indicate that ITO is stable under electrochemical processing [110]. However, to determine this for the specific processing conditions used in template formation, this was experimentally investigated using ITO coated glass-slides ( $R_s$ =4-8  $\Omega$ ) purchased from Digital Technologies, LTD. An aluminum thin film was deposited by magnetron sputter deposition and was anodized in sulfuric acid. The potential-time profile is shown in Figure 2-7. This result tends to indicate that alumina

was formed on the templates, however the noise during the end of pore propagation suggests the presence of an adverse chemical reaction at the alumina/ITO interface.

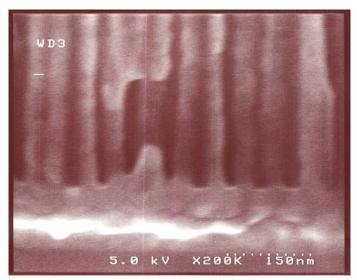

At the same time, the use of an aluminum/platinum/silicon structure was investigated. In this case, a 50 nm Pt film was deposited by electron-beam evaporation followed by a 500 nm Al film without breaking vacuum. The template was then anodized using a constant voltage and an unusual effect was observed. Instead of the rapid increase in resistance seen in every other material, the resistance remained constant, although a substantial amount of noise was detected. A top view and cross-sectional view of the fabricated structure is shown in Figure 2-8 and 2-9 respectively.

Figure 2-7: Potential time characteristic for the alumina formation on an ITO coated glass substrate.

Figure 2-8 shows that an ordered alumina template was formed for the Al/Pt/Si structure. The cross-sectional image shows that the pores are normal to the Pt layer and that the barrier layer is absent. This is confirmed by noting that the angle between the pore and the Pt layer is 90°. If the

barrier layer was in fact present, this would represent a singularity in the electric field distribution during anodization. Therefore, it appears clear that the use of the Al/Pt/Si structure both prevents the formation of an interfacial oxide layer and provides *in-situ* removal of the alumina barrier layer. The mechanism for the barrier layer removal is believed to be field-enhanced dissolution of the alumina and is caused by the termination of the electric field at the Pt layer. Therefore, since the resistance of the substrate and electrolyte is negligible, all the potential drop must occur across the barrier layer. Finally, after the barrier layer is removed, an electrolysis reaction occurs resulting in the generation of hydrogren and oxygen. This is believed to be the cause of the noise observed at the end of the Al/Pt/Si anodization process.

**Figure 2-8:** Top view of alumina pores formed on the Al/Pt/Si structure.

**Figure 2-9:** Cross-sectional image showing pores contacting the Pt layer.

The *in-situ* removal of the barrier layer with the Pt/Al/Si structure is a very significant result and was presented at the 2001 Electronic Materials Conference in South Bend, IN. This simplifies the problem of ensuring reliable electrical contacts to the semiconductor nanostructures, and enables the use of direct-current (DC) and under-potential (UP) deposition techniques. As will be shown in Chapter 3, the use of these electrochemical synthesis techniques can substantially enhance semiconductor material quality.

### 2.3 Standard Process Flow

The basic process flow for the fabrication of an alumina thin film directly on a silicon substrate with a single anodization step is described on the following pages:

#### **Substrate Cleaning**

2" p-type Si wafers with  $\{100\}$  orientation and 1-3  $\Omega$ -cm resistivity are used as the substrate for template formation. These wafers are then cleaned using SummaClean for 30 minutes at a constant temperature of  $60^{\circ}$  C. This step removes organic and heavy ion contamination. Then, any native oxide is removed with a 3 minute dip in 100:1 HF solution at room temperature. After a 10 minute rinse in DI water (18.2  $\Omega$ -cm), the substrates are dried with  $N_2$  and baked at  $130^{\circ}$  C for 30 minutes to remove moisture.

### **Contact Formation**

A back contact (170 nm) is deposited by magnetron sputter deposition using an 8" 99.999% Al main target at 1kW deposition energy for 3 minutes. The base pressure before sputtering is typically  $5 \times 10^{-6}$ , and the Argon flow rate is 100 sccm. After deposition, the back contact is annealed at  $450^{\circ}$  C for 30 minutes in an  $N_2$  atmosphere to ensure an ohmic contact and to enhance film adhesion.

## **Template Aluminum Formation**

Immediately after the back-contact anneal, the substrate is placed in the CVC Magnetron Sputter system and the system is pumped to a base pressure of less than  $1x10^{-6}$ . Deposition is carried out using the Al main target at an energy of 1kW. The deposition time is dependent on the thickness required for the final alumina template. After deposition, the substrate is annealed at  $400^{\circ}$  C for 30

minutes in an  $N_2$  atmosphere. The purpose of this step is to improve film adhesion. This does not appear to be required for prime silicon wafers, however it does eliminate the likelihood of adhesion problems when using test silicon wafers.

## **Anodization**

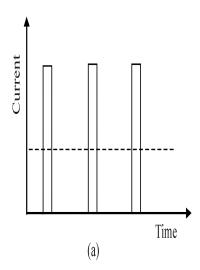

After the wafers have cooled, they are scribed and cleaved to form four separate samples for anodization. The anodization solution is 20% (v/v)  $H_2SO_4$  prepared by dilution from 98% double-distilled sulfuric acid. The acid is then chilled using a Masterflex peristalsis pump and Julabo chiller until the acid reduces a final temperature of  $3^{\circ}$  C. The temperature of the bath in the chiller at this point is  $-9^{\circ}$  C. The sample is then mounted in a custom designed Teflon apparatus [111] and inserted into the anodization solution. Anodization is then performed at either a constant current density (10-40 mA/cm²), or at a constant voltage (10-30 V). After the anodization is complete, the sample and apparatus are removed and rinsed in DI water for 10 minutes. The sample is then removed, rinsed in DI water, and dried with  $N_2$ .

# **Pore Widening**

To enhance etch uniformity, the sample is soaked in DI water for 12 hours before pore widening. The sample is then pore widened in a 5% phosphoric acid solution for 6 minutes. After the etch, the sample is removed, rinsed in DI water for 10 minutes, and dried with  $N_2$ .

# 2.4 Template Characterization

The alumina templates have currently been characterized by imaging, electrical and optical techniques. The specific results are discussed on the following pages:

#### 2.4.1 Imaging

Imaging of the template material is difficult due to the combination of three factors. First, the features of interest (pores) have diameters down to 4 nm. Second, the presence of pores in the template means that there is a relatively large height variation within the samples. Finally, alumina is a strongly insulating material. The combination of factors restricts imaging to the use of field emission scanning electron microscopes (FESEM), atomic force microscopes (AFM), and transmission electron microscopes (TEM).

### **TEM**

An early TEM image of pores on a silicon substrate is shown in Figure 2-10. While this technique provides the highest feature resolution, sample preparation requirements and expense limits its usefulness for routine template characterization.

### **FESEM**

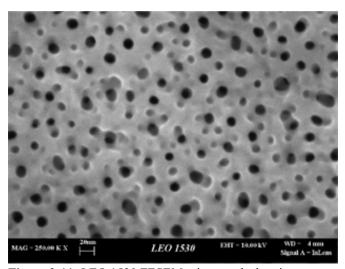

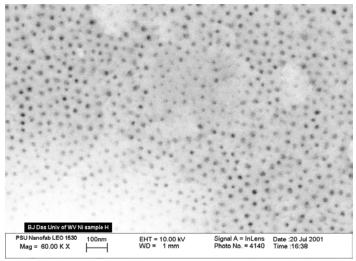

It has been determined that the optimum instrument for template imaging is the LEO 1530 FESEM that contains a Schottky type (ZrO-W) field emission source. This source provides the high beam brightness and low energy spread seen with cold-cathode field emission sources, while still

**Figure 2-10:** TEM image of pores in alumina. Average pore diameter is 13 nm.

providing low beam noise (1%), and low emission current drift (< 0.5%/hour). The field emission gun in the LEO 1530 uses a crossover-free electron path that maintains a high beam energy through the entire electron optical column. The electron beam is decelerated to the desired energy after the beam has passed through the scanning system. The combined effect of the crossover-free beam and the high beam energy minimizes statistical Coulomb interactions and transverse chromatic aberration at low beam energies. This provides a significantly increased resolution for low beam energies (2.5 nm at 1 kV). The magnification of this instrument is continuously variable between 20X to 900,000X, with an accelerating voltage adjustable between 200 V to 30 kV. A representative image from the LEO 1530 is shown in Figure 2-11.

**Figure 2-11:** LEO 1530 FESEM micrograph showing pores in an alumina template (not pore widened.)

In addition to the LEO 1530, a Hitachi 4500 cold cathode FESEM was used for work at the University of Notre Dame. The cold cathode can provide theoretically higher resolution than the LEO 1530, however this results in a significantly larger beam current density that increases charging in insulating materials. In addition, a cold cathode filament requires substantially lower vacuum pressure ( $<1x10^{-10}$ ) that can degrade instrument performance in a multi-user environment. A representative image from this instrument is shown in Figure 2-8.

### **AFM**

An image obtained using a Digital Instruments Atomic Force Microscope (AFM) is shown in Figure 2-12. It has been determined that the use of tapping mode provides the best images with this instrument due to the large surface topography. As a result of this topography, this technique does not provide the same image quality as an FESEM. However, it is valuable for providing quantitative surface roughness information, primarily for the starting aluminum films.

**Figure 2-12:** AFM image of an alumina template.

#### 2.4.2 Electrical Characterization

By the deposition of a metal top contact to the alumina template, a metal-insulator-silicon (MIS) structure can be formed. Since this type of structure is sensitive to the insulator/semiconductor interface as well as to ionic charge in the insulator, it can be used to characterize average template properties. The characterization of alumina templates by CV analysis was carried out by the deposition of an array of aluminum top contacts on an alumina template by sputter deposition through a shadow mask. An image of a sample with the deposited top contacts is shown in Figure 2-13. After contact deposition, the current-voltage characteristics of the pads was evaluated to ensure that leakage current was below acceptable levels. Then, the capacitance was measured as a function of applied voltage using an HP LCR meter in collaboration with Christopher Garman. A typical CV scan is shown in Figure 2-14.

**Figure 2-13:** A typical sample for CV measurements. Small circular pads are aluminum top contacts.

To investigate the effect of pore widening on the alumina templates, C-V analysis was performed on a set of silicon wafers as a function of current density and pore widening. Then, from the observed C-V behavior, the flat-band voltage was determined. A graphical representation of this analysis shown in Figure 2-15 demonstrates—that pore widening significantly reduces the distribution in flat-band voltages. The most likely explanation for this behavior is that pore widening removes the non-uniform pore nucleation layer from the templates.

Figure 2-14: A typical Capacitance-voltage characteristic for the template.

**Figure 2-15:** Flatband voltages obtained from CV data of pore-widened and pore-unwidened samples.

# 2.4.3 Optical Characterization

Photoluminescence characterization of alumina templates has been previously shown to result in emission at approximately 460 nm and has been attributed to the incorporation of inorganic anions within the alumina pore sidewalls [99]. Since CV characterization shows a reduction in flatband voltage with pore widening, the effect of pore widening on the alumina template PL was investigated. PL was performed at the Department of Physics at West Virginia University at 5 K and with an excitation wavelength of 325 nm. The results are shown in Figure 2-16. These results show a blue-shift in PL peak wavelength and an increase in emission intensity with increased pore widening. The mechanism for this behavior is not yet clear. However, it has been observed that in the case of porous silicon, storage in Fluroware containers results in blue emission with a narrow spectral range. This is attributed to the outgassing of trace amounts of hydrocarbons that are then

absorbed in the large surface area material. This may provide an explanation for the observed PL data. The samples for this investigation were stored in Fluroware. In addition, pore widening is known to result in an opening of the tops of the pores, resulting in increased surface area. This can be investigated more thoroughly by performing FTIR characterization and looking for the signature absorption bands of CH<sub>3</sub> and CH<sub>2</sub> at between 2939 and 2965 cm<sup>-1</sup> [112].

**Figure 2-16:** Photoluminescence characterization of pore-widened templates.

# 2.5 Silicon Carbide

The ability to selectively synthesize carbon nanotubes on a silicon carbide substrate is currently being investigated in collaboration with the NASA Glenn Research Center. To accomplish this, it is necessary to be able to deposit a periodic array of Ni dots on the silicon carbide substrate. As part of this effort, the ability to form a template on silicon carbide was verified, and Ni was electrochemically deposited into the template pores. A potential time characteristic for the template formation is shown in Figure 2-17 and an FESEM image of nickel deposited into an alumina templates is shown in Figure 2-18.

# Voltage Time characteristics for anodization of aluminum on Silicon Carbide T=5C I=15 mA/cm2

Figure 2-17: A typical voltage-time curve for the anodization of aluminum on SiC substrate.

**Figure 2-18:** FESEM top image of nickel deposited in the pores of alumina thin film template

# **Chapter 3**

# **Electrochemical Synthesis**

Electrodeposition of semiconductor material is a particularly attractive technique since it is possible to fabricate uniform films over a large area with low cost, high throughput, and scalability [113]. In addition, the ability to fabricate compositionally modulated or nonequilibrium alloys raises the possibility of fabricating non-traditional semiconductor materials [114]. Finally, for the special case of nanostructure fabrication using alumina templates, the presence of an applied electric field allows enables the filling of high aspect ratio pores.

In this chapter, the use of electrochemical techniques for the fabrication of semiconductor nanostructures will be discussed. In addition, characterization results for the synthesis of CdS quantum wires using these techniques will be presented.

### 3.1 Chemical Deposition

The most basic method of semiconductor synthesis in the alumina template pores is referred to as the "Miller" process and was developed at the University of Notre Dame in the early 1990's. In this approach, after template formation, a small AC current is applied to the template to deposit a layer of sulphide ions along the pore walls. Then, the templates are immersed in the appropriate salt solution (i.e. CdCl<sub>2</sub>) at 100° C. Chemical analysis indicates the presence of both species (Cd, S) in the pores. However, photoluminescence characterization reveals a very broad emission spectrum. It is the current belief of the developer of this technique that at best only a thin film of CdS is formed

along the pore walls due to the limited supply of sulphide ions. However, this technique is still used by Bandyopadhyay at the University of Nebraska [115].

## 3.2 Nonaqueous AC Deposition

The primary method of semiconductor deposition into alumina templates formed on bulk aluminum substrates is nonaqueous AC deposition. Nonaqueous techniques are the method of choice for semiconductor deposition since they allow a greater flexibility in the choice of chemical precursors, do not etch either the substrate or deposited material, and avoid the generation of hydrogen through electrolysis of water [113]. The primary solvent used for nonaqueous deposition of II-VI semiconductor material is Dimethyl Sulfoxide (DMSO).

The deposition of II-VI quantum wires into alumina templates using AC deposition was systematically investigated by Moskovits starting in 1996 [116, 117]. In their deposition method, CdCl<sub>2</sub> and elemental sulphur are dissolved in DMSO. The material is then deposited at a temperature ranging from between 100-160 C with an applied AC current. The use of an AC current is required due to the presence of the alumina barrier layer. From his investigation, Moskovits was able to conclude that:

- Uniform CdS quantum wires were formed without the presence of structural voids.

In addition, the quantum wires synthesized retained the template pore dimensions.

- 2) Oriented growth of CdS occured with the c-axis phase of the hexagonal wurtzite phase aligned normal to the substrate surface.

3) Electrochemical deposition into the alumina template increased CdS crystal order and reduced strain when compared with CdS deposition on a bulk Pt electrode.

In his work, Moskovits concludes that the presence of nanometer scale pores results in electrochemical growth from a single nucleation site due to the small pore diameter.

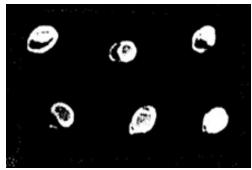

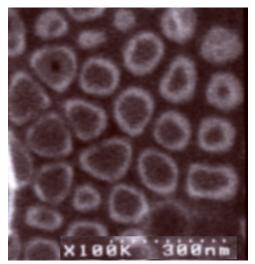

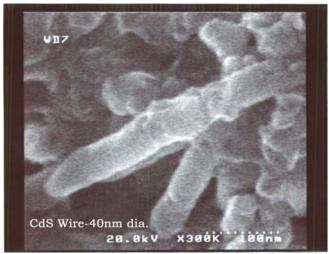

While Moskovits concentrated on structural characterization of the CdS synthesized in the templates, he did not perform optical characterization of the material. Therefore, CdS was synthesied in an alumina template with dimensions of 15 nm and 40 nm by the technique discussed earlier in this section. FESEM images with the templates partially and completely removed by a 10% NaOH etch are shown in Figures 3-1 and 3-2 respectively.

**Figure 3-1:** FESEM Image of 40 nm CdS quantum wires with alumina template removed.

**Figure 3-2:** 40 nm CdS wires with the alumina template completely dissolved.

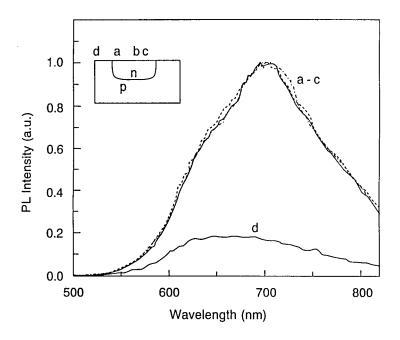

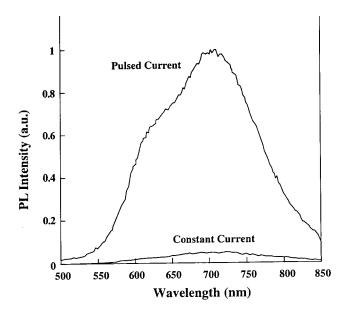

The CdS templates were then characterized by low temperature (5 K) photoluminescence and Raman measurements by Lijun Wang in the Department of Physics at WVU. The PL results shown in Figure 3-3 indicate intense luminescence with a relatively narrow spectral range with a peak energy below the bandgap. At peak position the 40 nm wire luminescence is less intense and shows emission that is consistent with the band-edge of CdS. The luminescence from the 15 nm wires is more intense and the below band-gap feature shows structure with what appears to be a doublet. There is no evidence of significant band-edge luminescence in this sample. There does not appear to be a shift in PL peak position between the two samples.

Raman measurements were taken with the 514.5 nm output from an argon ion laser and the beam was focused to a spot size of approximately 10 microns. The results are shown in the range of 300 cm<sup>-1</sup> in Figure 3-4 and between 1000 to 4000 cm<sup>-1</sup> in Figure 3-5. There is a significant enhancement in Raman scattering for the sample with 15 nm diameter at the value of the first LO phonon in CdS (300 cm<sup>-1</sup>). Weak scattering is observed for the 40 nm sample at approximately 313 cm<sup>-1</sup>. The

decrease in the first LO phonon position with decreasing wire size is consistent with the measurements of Moskovits who reported a shift from 308 cm<sup>-1</sup> to 300 cm<sup>-1</sup> for wires with dimensions less than 10 nm. It is important to note here that the quoted values for quantum wire size of 15 nm and 40 nm is based on measurements of the template pore diameter, rather than actual wire diameter. In the case of Moskovits, quoted dimensions are actual quantum wire size.

Figure 3-3: PL characterization of CdS wires with diameters of 40 and 15 nm.

**Figure 3-4:** Raman shift of CdS quantum wires with 15 nm (Sample 2) and 40 nm (Sample 1) diameter near the first LO phonon.

**Figure 3-5:** Raman shift of CdS quantum wires with diameters of 40 nm (Sample 1) and 15 nm (Sample 2).

The broad peak in the range between 1000-4000 cm<sup>-1</sup> was observed by Balandin in samples fabricated using the deposition technique discussed in Section 3.1 and was attributed to intersubband transitions in CdS quantum dots. This feature is not observed in the 40 nm sample and therefore may indicate the onset of quantum confinement for the 15 nm diameter sample. The series of sharp lines around 1300 cm<sup>-1</sup> has been attributed by Giles and Wang to luminescence from trace amounts of rare earth impurities.

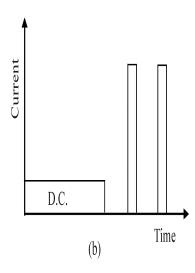

# 3.3 DC Nonaqueous Deposition